2023-2025

# Master of Science in Electrical Engineering with Specialization in Integrated Circuits

# "A Training from Idea to Product Design"

## **Salient Features and Objectives:**

- Pioneer of Integrated Circuits (IC) design graduate program in Pakistan.

- First time in Pakistan an academic opportunity for IC designing on Licensed Cadence Tool Suite.

- Well Established collaboration with public and private industrial partners.

- Hands on design experience on TSMC officially provided 65nm, 130nm and 150nm CMOS PDKs.

- Fully developed ICD lab and curriculum with six full time faculty members with degrees in IC design and cumulative experience of over a dozen of IC tapeouts.

- A bridge between the industry-and-academia to pave the way to FAB-less innovations resulting in commercialization IC design houses.

- 25 fully industrial funded MS students graduated in Fall-2021, hired by public sector organization.

- Taped out 8 Projects on two IC's by MS students graduated in Fall-2021.

- Active Participation in IEEE SSCS PICO Design Contest, 3 projects granted in 2021, 8 projects granted in 2022.

## MS EE Program Objectives:

This program prepares a graduate in Electrical Engineering to acquire expertise in the area of Integrated Circuits. This program is fully dedicated and focused on the IC design knowledge and skills, each student in this program will do the real world tape out from project conception to the working silicon microchip under the guidance of faculty supervisor from university and industry experts.

## Eligibility:

Bachelor's degree in a relevant engineering discipline (Electrical, Electronics, Telecommunications, or Computer engineering, etc.), recognized by Pakistan Engineering Council (PEC).

Minimum CGPA of 2.0, Preferably 2.5 (on a scale of 4.0) or at least 60% marks.

#### Scholarships:

Full and partial fee waiver for high achievers and deserving candidates

A student has the option to pursue MS by undertaking either a 6-credit hour MS Thesis or MS Project, spread over two regular semesters.

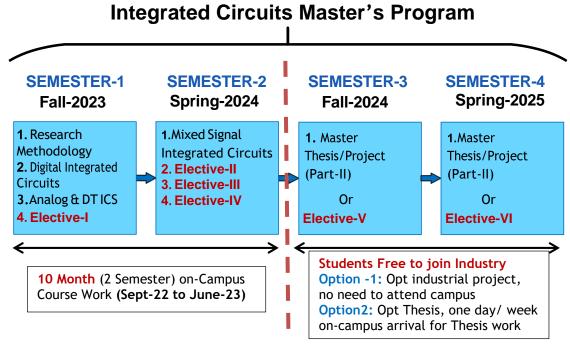

#### **Tentative Study Plan:**

| Semester I |                 |            |  |  |

|------------|-----------------|------------|--|--|

| SS 505     | 3               |            |  |  |

| EE         | Core Course-II  | 3          |  |  |

| EE         | Core Course-III | 3          |  |  |

| EE         | Elective -I     | 3          |  |  |

|            | Total           | 12 credits |  |  |

| Semester-II |                |            |  |  |

|-------------|----------------|------------|--|--|

| EE          | Core Course-IV | 3          |  |  |

| EE          | Elective -II   | 3          |  |  |

| EE          | Elective -III  | 3          |  |  |

| EE          | Elective -IV   | 3          |  |  |

|             | Total          | 12 credits |  |  |

| Semester-III |              |         |  |

|--------------|--------------|---------|--|

| EE 591       | MS Thesis-I/ | 3       |  |

|              | Project - I  |         |  |

|              | Total        | 3       |  |

|              |              | credits |  |

| Semester-IV |                             |           |  |

|-------------|-----------------------------|-----------|--|

| EE 592      | MS Thesis-II/<br>Project-II | 3         |  |

|             | Total                       | 3 credits |  |

The total credits of the MS programs are 30, which includes the 24 credits of the course work including the 03 credit Research Methodology Course and 06 credits of the MS thesis/project work.

Note: Registration in "Thesis - I / Project - I" is allowed provided the student has:

- Earned at least 15 credits

- Passed the "Research Methodology" course;

- CGPA is equal to or more than 2.5

#### **Recommended Electives:**

- 1. Signal Integrity, Packaging and SoC Design

- 2. Digital ICs Synthesis & Physical Backend Design

- 3. Design Project: From Schematic to Chip Tapeout

- 4. Universal Verification Methodology (UVM)

- 5. Advanced Digital Signal Processing (ADSP)

- 6. Advanced Embeded Systems

## MS (Electrical Engineering - Specialization in Integrated Circuits):

Core Courses for MS-EE with Specialization in Integrated Circuits:

- 1. Research Methodology (03 Credits) (HEC Requirement)

- 2. Digital Integrated Circuits (03 Credits)

- 3. Analog & DT Integrated Circuits (03 Credits)

- 4. Mixed Signal Integrated Circuits (03 Credits)

Elective Courses (One must select minimum of 4 courses from this list of Electives)

- 1. Signal Integrity, Packaging and SoC Design (03 credits)

- 2. Digital ICs Synthesis & Physical Backend Design (03 Credits)

- 3. IC Design Project: From Schematic to Chip Tapeout (03 credits)

- 4. Universal Verification Methodology (UVM) (03 Credit)

- 5. RF Integrated Circuits (03 Credits)

- 6. Advance Microwave Engineering (03 Credits)

- 7. Advance Embedded Systems (03 Credits)

- 8. Advance Digital Signal Processing (03 Credits)

- 9. Advanced Wireless Communication (03 Credits)

- 10. IC Marketing and Business Management (03 Credits)

## Teaching Faculty:

Teaching faculty is hands on IC designer with cumulative experience of over dozen IC tape outs in different technologies.

For CVs of faculty, please see (<a href="http://isb.nu.edu.pk/rfcs2/team.htm">http://isb.nu.edu.pk/rfcs2/team.htm</a>)

- Prof. Dr. Rashad Ramzan

- Dr. Hassan Saif

- Dr. Shazad Saleem

- Dr. Arshad Hassan

- Engr. Hamza Atiq (MS EE)

- Engr. Daniyal Ali (MS EE)

- Engr. Ali Sabir

- Engr. Usama Liaquat

## 04 Compulsory Courses (12 Credit Hours):

- 1. Research Methodology: The course is mandatory for all graduate programs offered under HEC umbrella. The course covers central aspects of the research process, as well as principles and questions related to sate of art search, research planning, problem formulation, statistical data analysis, quality assessment, presentation of a research project, and research ethics. (03 credits; HEC requirement)

- 2. Digital Integrated Circuits: Review of integrated circuit fundamentals, CMOS Device Characteristics, Layout Rules, CMOS Inverter, Basic Gates, Combinational Logic Multiplexers, Transmission Gates, Sequential logic circuits, Latches, Flip Flops, Adders, Multiplier, Accumulators, Memory cells, Layout strategies, Basic of Logic synthesis and use of CAD tools.

- <u>Lab Tutorials</u>: Design of Basic Logic Gates, Flip Flop, Adders, Multiplexer, Demultiplexer, Memory Cells, Complex Circuits, and layout in cell library format in Cadence tool suite. (03 credits)

- 3. Analog & DT Integrated Circuits: Review of fundamentals, Analog building blocks, CMOS Device and Noise Fundamentals, Single-stage (CS, CG, CD), Differential pair and multistage amplifiers, CMOS operational amplifier, Noise in CMOS Circuits, Feedback Principles, Current Sources and Current Mirrors, MOS Switched- Capacitor (SC) circuits, OTA, and Gm cells

- <u>Lab Tutorials</u>: CMOS DC Analysis, Common Source Amplifier, Common Gate Amplifier, Multi Stage Amplifiers, Common Drain Amplifier, CMOS Current Mirrors, Differential Amplifiers, Two Stage Op-Amp, CMOS Noise Analysis, Advanced Layout Techniques in Cadence Tool Suite. (03 credits)

- 4. Mixed-Signal Integrated Circuits: Non-Linearity and mismatch, CMOS Processing Technology, Layout Fundamentals, Sample & Hold Circuits, Voltage Comparators, Band-gap References, Data converters Fundamentals and Performance Metrics, Nyquist Digital-to-Analog Converters, Nyquist Analog-to-Digital Converters, Z-Transform, Oversampling ΣΔ Data Converters, PLL and Frequency Synthesizers

- <u>Lab Tutorials</u>: Advanced op-amp Design & Simulation, CMOS Comparators Design, Bootstrap Circuits Design, Switched Capacitor Circuits Design, Discrete circuit Layout Techniques, Nyquist Rate DAC Design, Nyquist Rate ADC Design, Sigma-Delta Converters, Oscillator & PLL circuits, Bandgap Reference Circuits in Cadence tool suite. (03 credits)

## **Elective Courses (12 Credit Hours):**

- 1. Signal Integrity, Packaging and Chip Design: Signal Integrity Principals, Chip interconnect and Transmission Lines, PCB and IC Materials, Impedance Matching, Power Distribution Network, Parallelism & Cross Talk. EMI and EMC, Reflections and Termination and IO Pads, On-Chip Passives, ESD Protection Management, IC and Discrete Component Packaging, Thermal Consideration, IC Failure and Reliability, Microsystems Packaging and Applications.

- <u>Lab Tutorials</u>: Impedance Matching using Lumped Model, Impedance Matching using Microstrip Model, EMC and TL Discontinuity Modeling and Simulation, Bond wire Modeling and Simulations, Power Distribution Network Modeling, Parallelism Transmission Line Modeling & Analysis, Crosstalk and Noise Analysis, EMI/EMC Interference Analysis, On-Chip Passives and Corner Analysis.

- 2. RTL Synthesis, & Digital Backend: Basics of HDL (Verilog) Coding. Synthesizable RTL, State Machine Design, HDL Testbench Design, RTL Code Compilation Scripts Development, Placement and Routing, Static Timing Analysis (STA), CLK Insertion, RISC-V for Embedded Systems. (03 credits)

Lab Tutorials: Introduction to Verilog and Modelsim, State Machine Design, RTL Synthesis using Standard Cell Libraries, Place, Route, and Static Timing Analysis, Physical Layout using Cadence Genus, Innovus etc. Fullchip Physical Verification (DRC/LVS)

- 3. IC Design Project: From Schematic to Chip Tapeout: Project selection, Pre-study, and Floor planning, Schematic/HDL Capture, Architectural level, Gate/Transistor level, Synthesis and simulations, Pad Frame Selection and Design, Library Mapping and Optimization, Analog ad Digital Layout Strategies, DRC, Post-Layout Verifications, Back Annotations, Generation of Mask data-base for Chip-Layout, Final Tapeout. (03 credits) This is hand-on IC design course, which needs intensive LAB work.

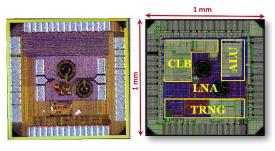

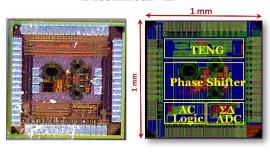

## Spring 2021 Taped out Projects Layout and Die Photographs

## Kamal-1

**PICO 2021 TAPEOUTS: 3 Projects**

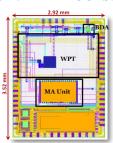

## Kamal-2

PICO 2022 TAPEOUTS: 6 Projects

Page **5** of **8**

MS EE with Specialization in Integrated Circuits

- 4. Universal Verification Methodology (UVM): Understand the UVM hierarchies and various components needed to build a comprehensive UVM Testbench, Design and implement various testbench components, such as driver, monitor, sequencer, agent, environment, scoreboard, coverage, and environment, and understand the configuration databases, factory override, Transaction Level Modeling (TLM), understand virtual sequences and virtual sequencers and Building a framework for UVM Testbench. (03 credits)

- 5. RF Integrated Circuits: Basics Concepts of RF Electronics, Linearity (1dB CP and IIP3) and noise (Noise Figure) in radio circuits, High frequency model of the CMOS and BJT circuits, IC technology suitable for radio circuit design, Radio Standards, Radio Transceiver Architectures, Radio Transceiver Calculations, Transmission lines and impedance matching, Wideband and Narrow band design issues, Low Noise Amplifiers (LNAs), Active and Passive Mixers, Voltage Controlled Oscillators and Phase Lock Loops, Power Amplifiers. (03 credits)

- 6. Advanced Microwave Engineering: Introduction to microwave engineering, microelectronics device and device models, Transmission lines theory, reflection and transmission analysis, Microwave network analysis, impedance matching networks and tuning, wideband impedance matching issues microwave resonators, Power Dividers and directional couplers, Microwave filters and their implementation, Noise in microwave circuits, Microwave amplifier design, Microwave oscillators and mixers circuits. (03 credits)

- 7. Advance Embedded Systems: Basics of processor architectures. Memory organization and caches. Worst-Case Execution Time (WCET) Analysis, Compositional Timing Analysis for embedded systems, Embedded software platforms, Performance analysis, memory hierarchy, buses, peripherals, Wireless Sensor Networks, Internet of Things, Embedded systems platforms: MCUs, DSPs, GPU, FPGAs, Code optimization, Factors affecting Execution time, Multi-tasking and real-time operating systems, Scheduling algorithms and their performance. (03 credits)

- 8. Advance Digital Signal Processing: Introduction, Discrete-time Fourier transform (DTFT), Sampling & reconstruction, Fast Fourier transform (FFT), Using z-transform to represent linear time-invariant (LTI) systems, Digital filter design fundamentals, IIR, FIR and CIC filter design and implementation, DSP algorithm implementation issues and optimization, Linear prediction and optimal linear filters, Power spectrum estimations. (03 credits)

- Lab Tutorials/Class Project: Implementation of FIR, IIR or CIC comb filter on FPGA.

- 9. Advanced Wireless Communication: Introduction to Wireless & Mobile Communications, Propagation Models, Channel Models, Channel Sounding, Equalization, Transmission & Multiple Access techniques: OFDM/OFDMA, SC-FDMA etc., space-time coding (STC), BLAST architecture, massive MIMO, MIMO-OFDM transceiver design, Current Wireless Standards: IEEE 802.11n/ac WiFi, 4G mobile: 3GPPLTE, 3GPPLTE-, 5G RAN, Satellite Communications. (03 credits)

- **10.IC** Marketing and Business Management: Trends in the IC business: Technology and manufacturing trends, Demand, applications and product trends. Market Appearances: The customers, overall Business cycles, The bull-whip effect), IC industry, supply & value chain, Geo distribution of Technology and fabrication centers, The dis-integration of the value chain, outsourcing trends, Managing the marketing function: The sources of product ideas, The role of standard and intellectual property, The strategic partnership, distributorship and matching supply with demand. (03 credits)

# Feedback from Industry:

#### Dr. Nasir (Deputy DG NECOP):

MS IC Design graduates from FAST-NU Islamabad campus are very professional and have good knowledge base in all domains (Digital, Analog, Mixed Signal and RF) of IC design. They have been trained using state of the art IC Design Tools. Having gone through the complete IC design and fabrication cycle during their MS through a tape out project using TSMC 65nm Technology has enhanced their confidence to take up real world IC Design projects. They are comfortably working with IC Design teams at NECOP giving valuable inputs. Their performance in the National IC Design Center at NECOP has enhanced our trust in home grown solutions for trained HR in the advanced field of IC Design. The level of their competence and confidence shows the quality of teaching and Lab work at NU FAST Islamabad campus in the field of IC Design.

#### Aziz ur Rehman (General Manger NECOP):

NECOP IC Design Fellows joined NIDC (NECOP) after completing their Master's degree in EE with specialization in IC design from NUCES, FAST Islamabad. The fellows are serving in the fields of analog/mixed signals and digital IC design. They have a sound understanding of Integrated circuit design and relevant theory. During this period, they acquired hands-on experience on the industry standard IC design tools leading to the tape-out of chips (e.g. KAMAL-1, KAMAL-2). KAMAL-1 and KAMAL-2 includes Fault tolerant CLB, Approximate ALU, True random number generator, mm-Wave LNA, AC logics, sigma delta converters, tribo electric nano-generator and mm-Wave phase shifter projects respectively. The courses were specifically designed to provide the students with a strong knowledge of electronics and IC design skills.

## Feedback from Alumni:

## Jaffar Hussain (Fellow MS IC Design):

After bachelors I was looking for graduate program that can enhance my technical skills in practical domain. The Master program in IC Design at FAST provided me that opportunity. IC design is a field in which Pakistan need qualified human resource and this Master program at FAST is working towards it. This program is perfect for, Engineers seeking indepth training from concept to tape-out in analog and digital IC design.

### M. Usman (Fellow MS IC Design):

I have very unique experience while studying IC Design at FAST-NU. It was the only program of its kind in Pakistan, where I was able to learn IC design from scratch to tape out. The program offered me a variety of skills including; design, plan, management, economy, and art of designing practical circuits, that are much needed while designing real world chips. Definitely, it is a lot of work, but the experience worth it.

#### Hamza Saleem (Fellow MS IC Design):

All the faculty members at FAST are dedicated, passionate and supporting, especially Prof. Rashad Ramzan. He's more than a teacher for me. He changed the way of thinking, helped me develop my intuitions about design concepts. Besides, I remember the time when I asked a question to Dr. Hassan via WhatsApp message. He called me back and discuss the issue briefly. I did several meetings with faculty about Tape-out project and thesis and remember the positive criticism and highlighting the design issues from faculty. In a nutshell, I learnt several new concepts and developed design intuitions under the guidance of all faculty member. One thing I must say! After working with the faculty, if you put your whole effort too, you will be a practical Chip designer.

# Our Group:

# Recent Group Achievement

In IEEE Chipathon (https://sscs.ieee.org/about/solid-state-circuits-directions/sscs-pico-design-contest) Skywater130 FREE Tapeouts contest 55 proposal were submitted from all over the world 22 were selected, 08 are from Pakistan and all of them are from FAST-NU RFCS2/ICD Lab (http://isb.nu.edu.pk/rfcs2/index.htm). Here are details of the proposals.

| Sr | Project Title            | Affiliation  | Link                                       |

|----|--------------------------|--------------|--------------------------------------------|

| 1  | CMOS Bandgap             | FAST-NU, ISB | https://platform.efabless.com/projects/874 |

|    | Voltage Reference        | *            | 30 - 30 - 30 - 30 - 30 - 30 - 30 - 30 -    |

| 2  | Spatial Sigma Delta      | FAST-NU, ISB | https://platform.efabless.com/projects/872 |

|    | ADC                      |              |                                            |

| 3  | Fast Transient           | FAST-NU, ISB | https://platform.efabless.com/projects/879 |

|    | Response DC/DC Conv.     |              | 35,1112                                    |

| 4  | Subthreshold Ultra       | FAST-NU, ISB | https://platform.efabless.com/projects/883 |

|    | Low Power SRAM           |              |                                            |

| 5  | Self-Interface           | FAST-NU, ISB | https://platform.efabless.com/projects/888 |

|    | Cancelation LNA          |              |                                            |

| 6  | Matrix Multiplier for Al | FAST-NU, ISB | https://platform.efabless.com/projects/889 |

|    | on Edge Applications     |              |                                            |

| 7  | Low Power                | FAST-NU, ISB | https://platform.efabless.com/projects/921 |

|    | Approximate Processor    |              |                                            |

| 8  | ReRAM Based DNN          | FAST-NU, ISB | https://platform.efabless.com/projects/904 |

The other 14 projects were selected from MIT-USA, UT Austin-USA, North Carolina University-USA, Austria, Egypt, and few more.

Page **8** of **8**