# IC Packages, Connectors and Vias

## Rashad.M.Ramzan, Ph.D FAST-NU, Islamabad

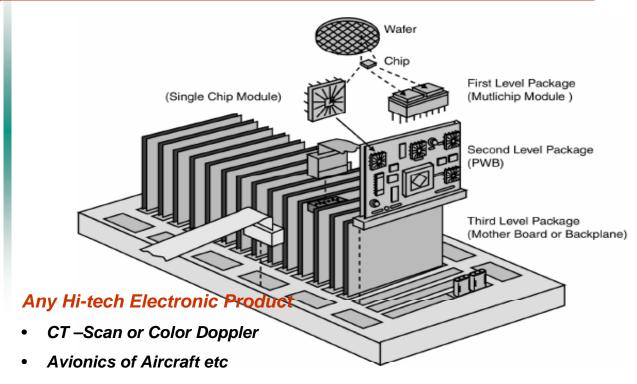

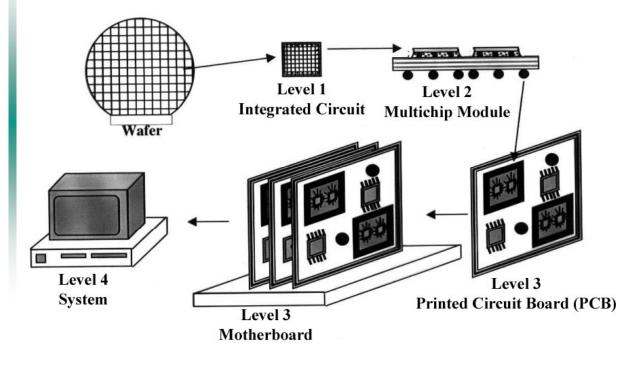

# System Packaging Hierarchy

High Speed PCB Design:Lecture-3

3

| Today's Topics                                            |

|-----------------------------------------------------------|

| • Why is packaging important ?                            |

| <ul> <li>Trends in packaging</li> </ul>                   |

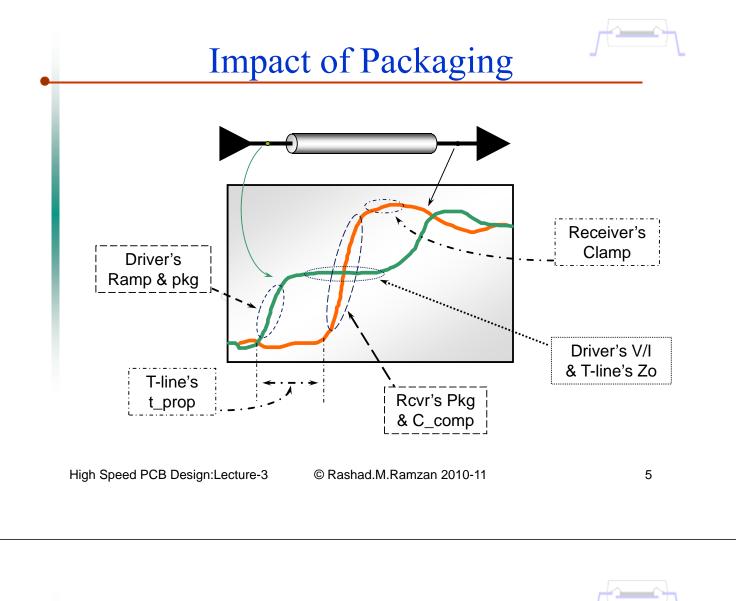

| <ul> <li>Impact on high speed signals</li> </ul>          |

| <ul> <li>Package and connector models</li> </ul>          |

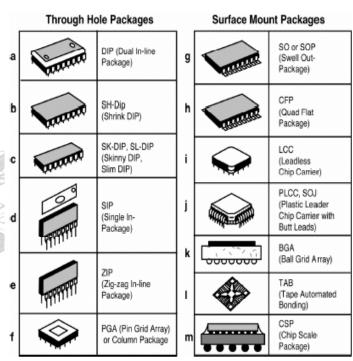

| – IC packages                                             |

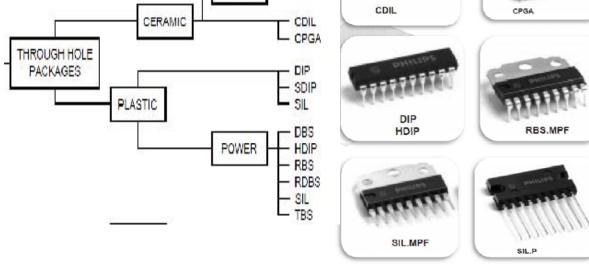

| Through hole                                              |

| Surface mount                                             |

| – Connectors                                              |

| Surface mount                                             |

| • Through hole                                            |

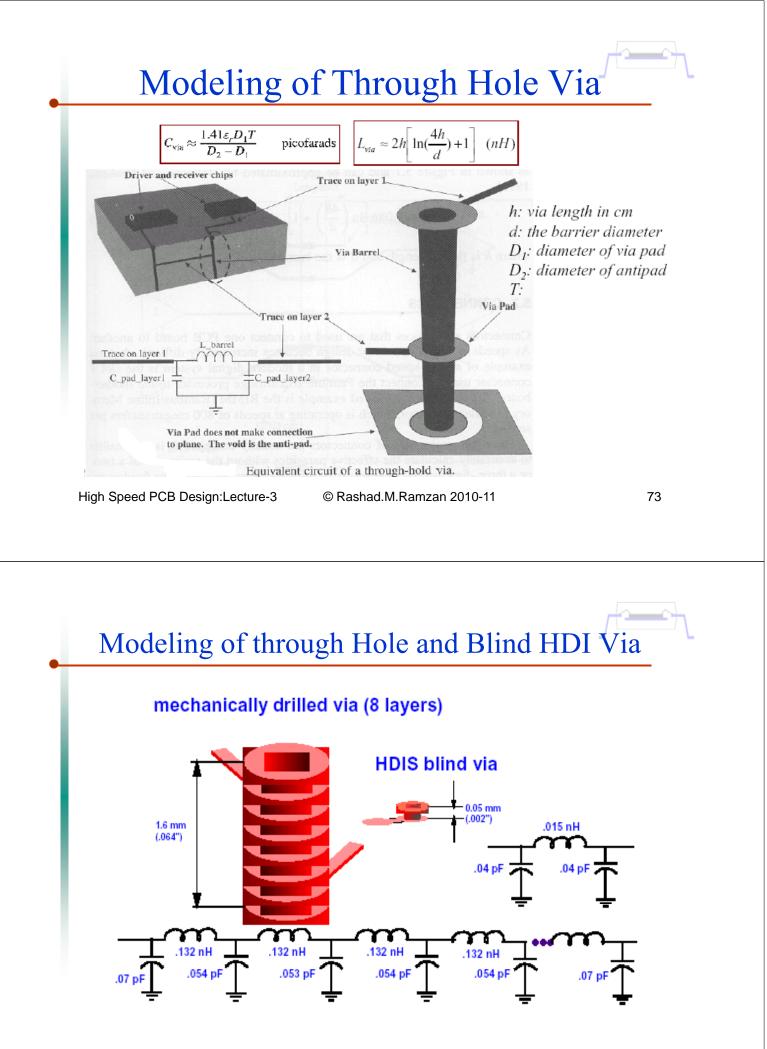

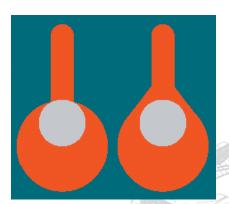

| Via and Via Types                                         |

| – Via Modeling                                            |

| <ul> <li>Standard Sizes, HDI</li> </ul>                   |

| High Speed PCB Design:Lecture-3 © Rashad.M.Ramzan 2010-11 |

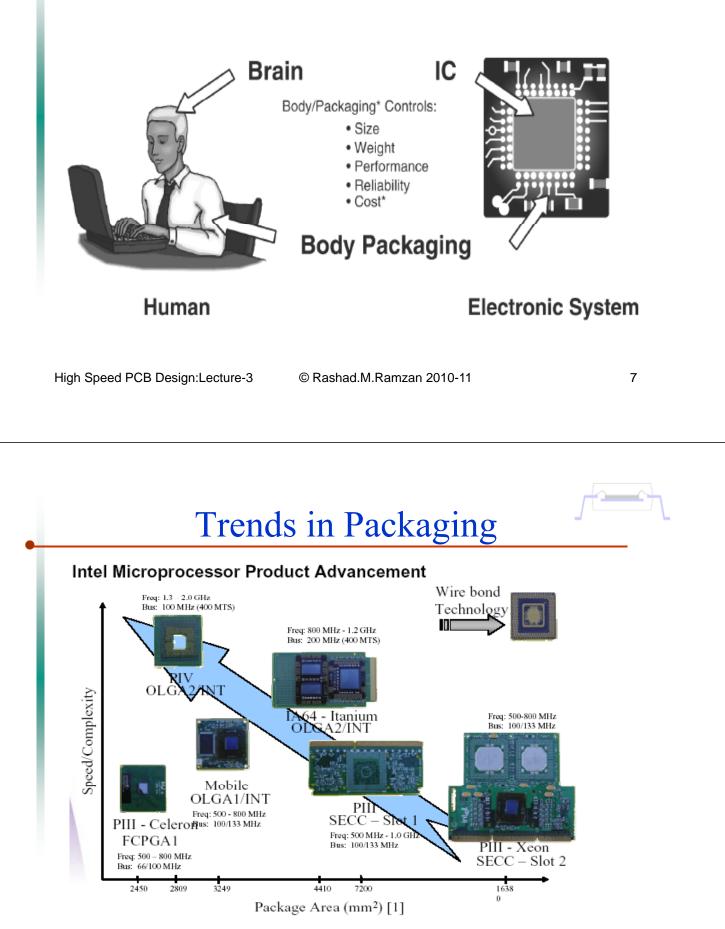

## Package Selection

- In PCB Design we use prefabricated package.

- If multiple package are available, decide based upon

- Temperature Rise (Commercial, Industrial, Military)

- Mechanical Strength (Avionics, Industrial or home appliance)

- Routability and Number of Layers

- Rework and troubleshooting

- Maximum CLK rate and Bus Speed

- EMI and EMC requirement

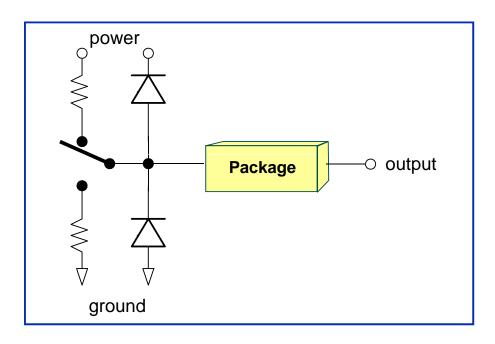

### Physical Connection with outside world

### Analogy Between Human and Electronics

## Levels of Packaging

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

9

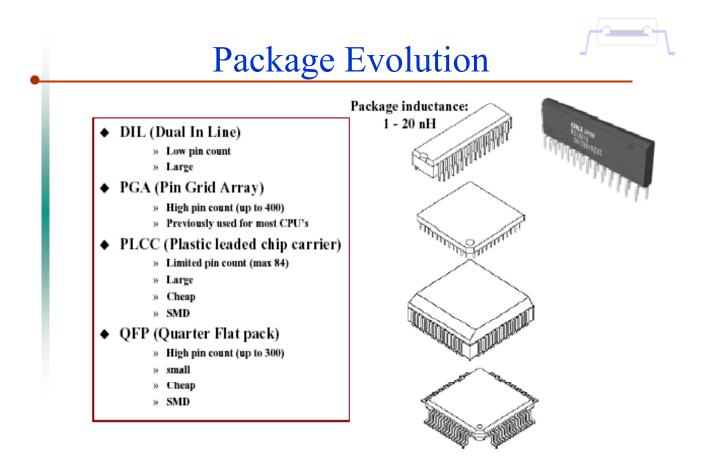

# Level 1:Single Chip Module (SCM)

### SCM families:

- THP

- Single (SIP)

- Dual (PDIP, CERDIP)

- Area Array: Quad (PGA)

SMD

- Dual: Small outline (SOJ, SOP, TSOP)

- Quad: Quad surface mount (PLCC, PQFP, CERQUAD)

- Area Array: Grid array (PGA, BGA)

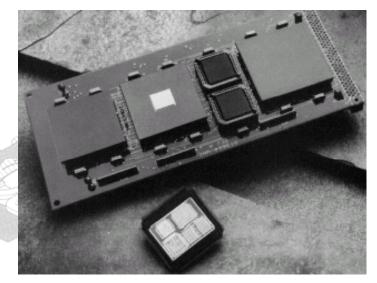

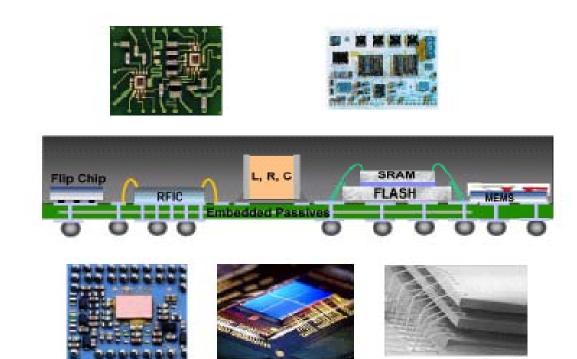

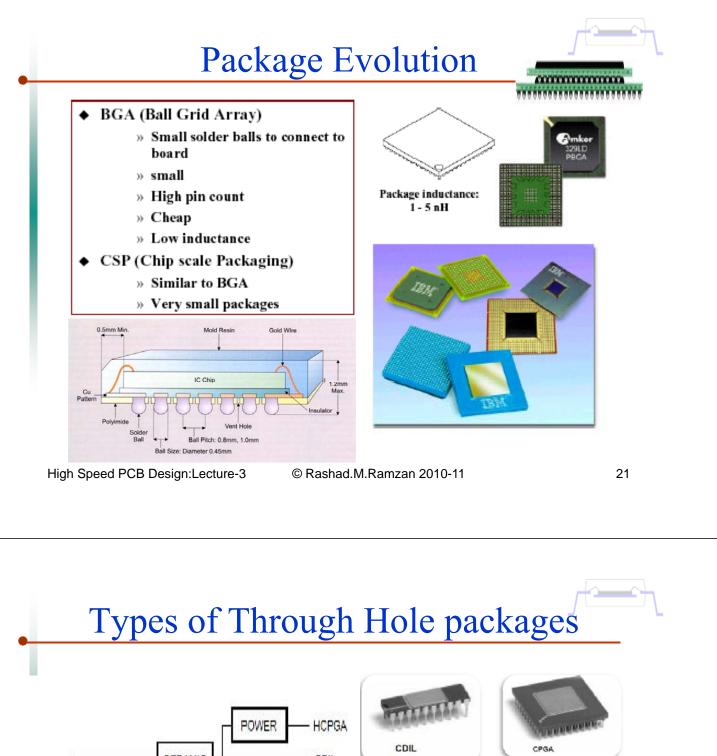

# Level 2:Multi Chip Module (MCM)

- MCM-L

- MCM-C

- MCM-D

- MCM-S

MCM-L 486 Processor Base of Similar Material like PCB

MCM-C Motorola 88110 CPU Ceramic Base

High Speed PCB Design:Lecture-3

MCM-D MMX Pentium on Aluminum Base covered by dielectric Polymide

© Rashad.M.Ramzan 2010-11

11

# Level 3 &4 :PCB and Final Product

- Level-3: PCBs, PWBs and back planes

- Level-4 : Systems Level

- Represents the final product/system and integration of PCBs

- Subassemblies like power supplies

- Items for user interface like CTR, Key Boards etc

- Special components like fans and transformers

- Wiring, cables and harnesses

- Protective enclosure

© Rashad.M.Ramzan 2010-11

### MCM vs PCB

- RISC processor on PCB

- Same Electrical Circuit on MCM

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

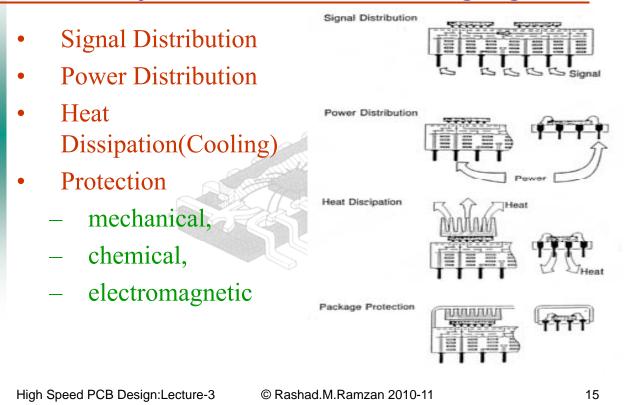

# Major Function of Packaging

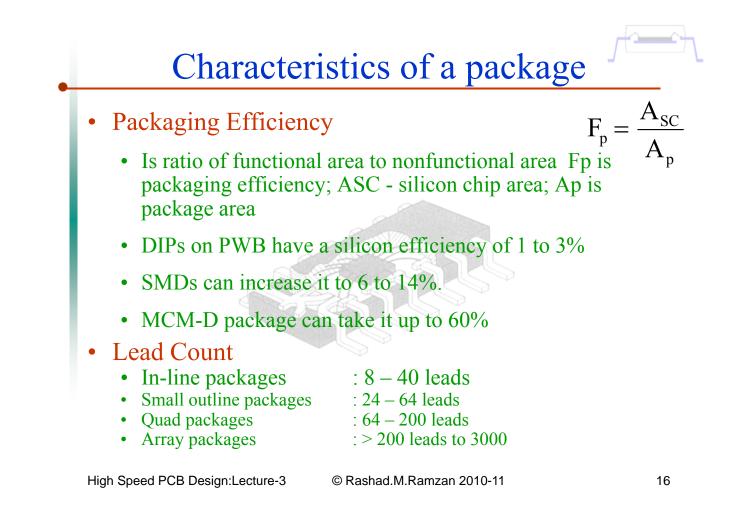

# Characteristics of a package

Thermal Performance

• Characterized by the thermal resistance, °C/Watt

$T_{junction} = T_{ambient} + q_{JA}.P$

$\mathbf{q}_{\mathsf{J}\mathsf{A}} = \mathbf{q}_{\mathsf{J}\mathsf{C}} + \mathbf{q}_{\mathsf{C}\mathsf{A}}$

Ceramic bodies give lower thermal resistance

• High-power ICs use heat sinks

- 7 x 7 mm chip dissipating 30 W results in a heat flux of more than  $6 \times 10^5$  W/m<sup>2</sup>

- Electrical Performance

- Delay

- Cross Talk

- Power Distribution

High Speed PCB Design:Lecture-3

Case to Ambient Thermal Resistance: 16-pin DIP in still air 80°C/W Junction to Case Thermal Resistance: 16-pin DIP in still air 34°C/W

© Rashad.M.Ramzan 2010-11

17

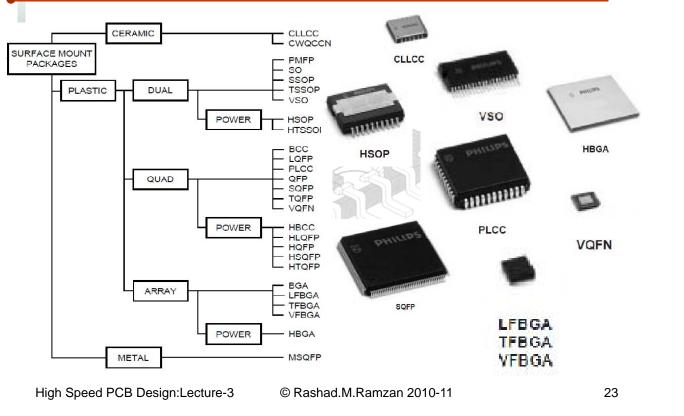

## Characteristics of a package

- Size and Weight

- Smaller size leads to higher silicon efficiency: BGA and CS packages

- Weight reduction is only through the choice of materials.

- Plastic bodies have less weight than Ceramic bodies

- 40-pin plastic DIP weighs about 6 gms

- -40-pin ceramic DIP weighs about 12 gms

-196-lead plastic quad flat pack weighs about 9 gms. High Speed PCB Design:Lecture-3 © Rashad.M.Ramzan 2010-11

# Characteristics of a package

- Reliability

- Reliability is influenced by

- Choice of materials

- Manufacturing processes

- Operating conditions and environment

- Reliability is enhanced by

- Hermetic packages

- Derating the devices

- Protecting interconnection with organic coatings

- Controlling the environment ambient to the device

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

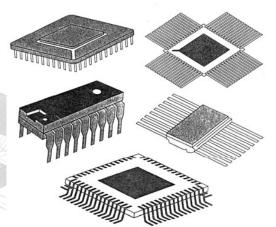

## Types of Surface Mount Packages

High Speed PCB Design:Lecture-3

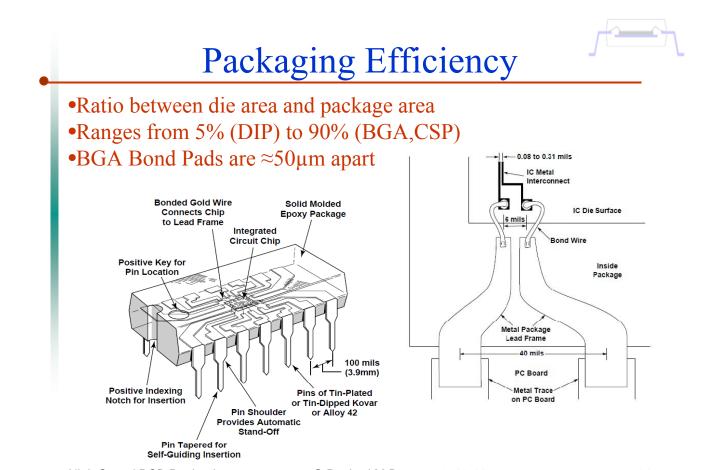

# Routing Complexity α Package Type

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

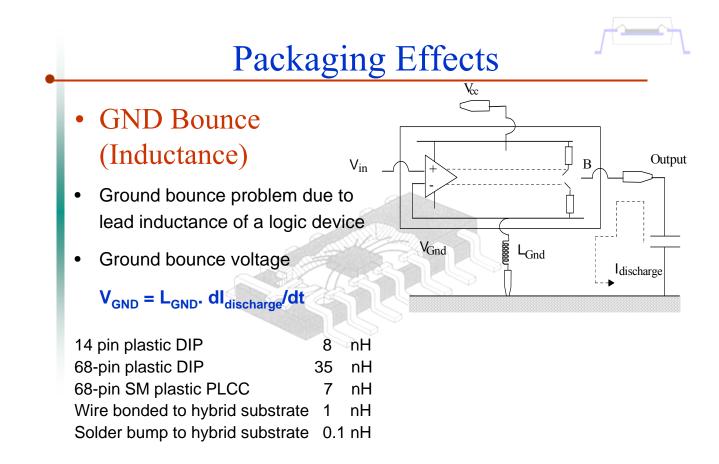

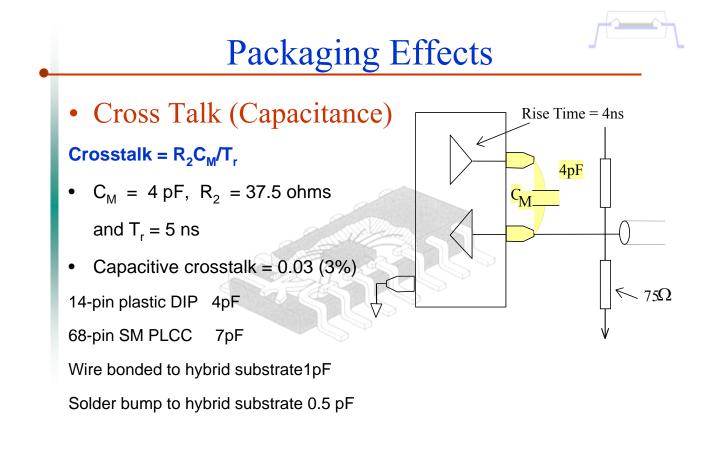

## **Packaging Effects**

|   | h |  |

|---|---|--|

|   |   |  |

| - |   |  |

|             |                | al IC packages<br>ad inductance |                |  |

|-------------|----------------|---------------------------------|----------------|--|

| 14-pin DIP  | 3.2 - 10.2 nH  | 14-pin SOIC                     | 2.6 - 3.6 nH   |  |

| 20-pin DIP  | 3.4 - 13.7 nH  | 20-pin SOIC                     | 4.9 - 8.5 nH   |  |

| 40-pin DIP  | 4.4 - 21.7 nH  | -                               |                |  |

| 40-pin TAB  | 1.2 - 2.5 nH   | 208-pin QFP                     | 5.31 - 8.74 nH |  |

| 44-pin QFP  | 6.07 - 7.06 nH | 100-pin QFP                     | 6.69 - 7.96 nH |  |

| 20-pin PLCC | 3.5 - 6.3 nH   | 119-pin PBGA                    | .15 - 5.7 nH   |  |

| 28-pin PLCC | 3.7 - 7.8 nH   | 249-pin PBGA                    | .13 - 5.1 nH   |  |

| 44-pin PLCC | 4.3 - 6.1 nH   | 624-pin CBGA                    | .5 - 4.75 nH   |  |

| 68-pin PLCC | 5.3 - 8.9 nH   | 456-pin PBGA                    | .2-5.8 nH      |  |

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

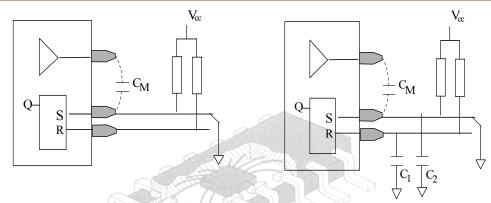

### Packaging Effects

### • High-impedance input problem:

Without C1 and C2 the impedance of R1 & R2 are high (~10k)Crosstalk factor = 8 C1 and C2 reduce the impedance of the receiving circuit at high frequencies Crosstalk factor =  $C_M/C1$ .

If C1 is set to 0.01 mF, crosstalk = 0.0004.

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

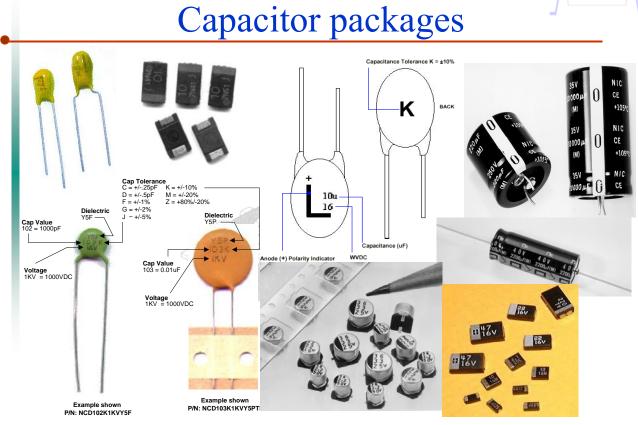

### Packages Types

- Packages for passive components

- Package for discrete components

- Package for ICs

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

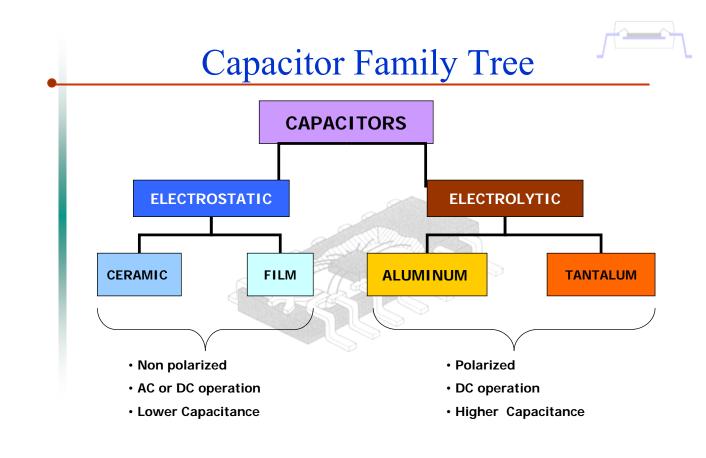

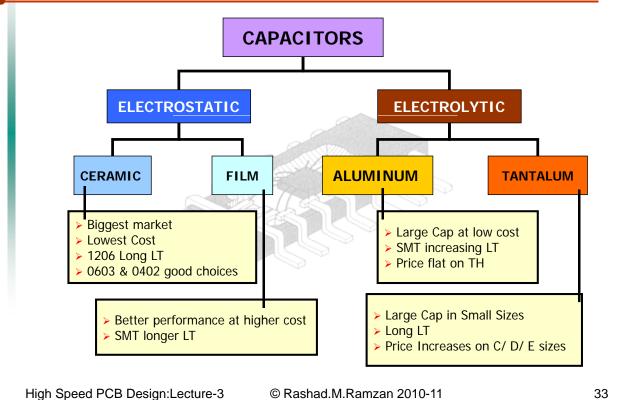

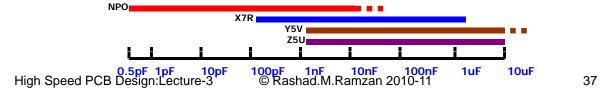

# Capacitor Family Tree

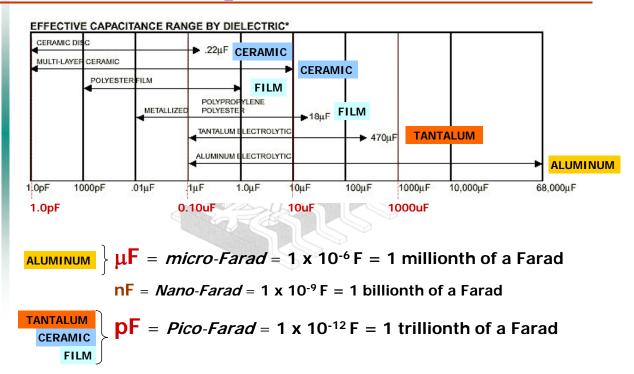

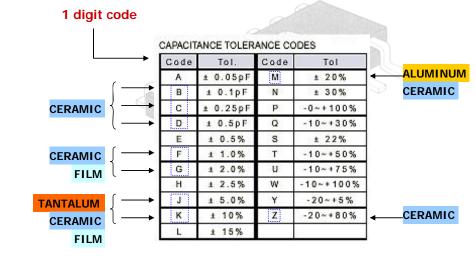

**Capacitor Values**

The allowable window - limits that the capacitors' +25°C (room temperature) capacitance value will be within.

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

35

## **Thermal Characteristics**

Standard Temperature Coefficients (TC) of ceramic capacitors:

| Low Temperature Limit | High Temperature Limit        | Maximum Allowable<br>Capacitance Change<br>From +25°C (0 VDC) |

|-----------------------|-------------------------------|---------------------------------------------------------------|

| <b>X</b> = −55°C      | <b>5</b> = +85°C              | <b>F</b> = ±7.5%                                              |

| <b>Y</b> = -30°C      | <b>6</b> = +105°C             | <b>P</b> = ±10%                                               |

| <b>Z</b> = +10°C      | 7 = +125°C                    | <b>R</b> = ±15%                                               |

| •                     | $8 = +150^{\circ}C$ (SPECIAL) | <b>S</b> = ±22%                                               |

| Ī                     |                               | <b>T</b> = +22% / -33%                                        |

|                       |                               | <b>U</b> = +22% / -56%                                        |

|                       |                               | <b>V</b> = +22% / -82%                                        |

|                       | <b>X7R</b> = ±1               | 5% ΔC over -55°C ~                                            |

**/ R** = ±15% ∆C over -55°C ~ + 125°C

Aluminum Electrolytic styles have TC of ±20% over -40°C to +105°C

Tantalum Electrolytic styles have TC of ±5% over -55°C to +85°C

Film styles have TC of ±7% over -40°C to +105°CHigh Speed PCB Design:Lecture-3© Rashad.M.Ramzan 2010-11

## **Capacitor Range**

### **Multilayer Ceramic Chip Capacitor**

Temperature Coefficients:

| тс  | Capacitance<br>Range | Capacitance<br>Value Code | Voltage<br>Range   | Standard<br>Tolerance |

|-----|----------------------|---------------------------|--------------------|-----------------------|

| NPO | 0.5pF ~<br>0.056uF   | 0R5 ~ 563                 | 25VDC ~<br>1KVDC   | (J)<br>+/-5%          |

| X7R | 100pF ~ 2.2uF        | 101~ 225                  | 16VDC ~<br>1000VDC | (K)<br>+/-10%         |

| Y5V | 1000pF ~ 10uF        | 102 ~ 106                 | 16VDC ~<br>50VDC   | (Z)<br>-20%/+80%      |

| Z5U | 1000pF ~ 10uF        | 102 ~ 106                 | 16VDC ~<br>50VDC   | (M)<br>+/-20%         |

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

## Capacitor Dimensions SMD

|                                                            | English | Metric | Length        | Width         |  |

|------------------------------------------------------------|---------|--------|---------------|---------------|--|

| 0402                                                       | 0402    | 1005   | 1.0mm (0.04″) | 0.5mm (0.02″) |  |

| 0803                                                       | 0603    | 1608   | 1.6mm (0.06") | 0.8mm (0.03″) |  |

| 0805                                                       | 0805    | 2012   | 2.0mm (0.08") | 1.2mm (0.05″) |  |

| 1206                                                       | 1206    | 3216   | 3.2mm (0.12") | 1.6mm (0.06″) |  |

| 1210                                                       | 1210    | 3225   | 3.2mm (0.12") | 2.5mm (0.10″) |  |

|                                                            | 1812    | 4532   | 4.5mm (0.18") | 3.2mm (0.12") |  |

| 1812                                                       | 2225    | 5764   | 5.7mm (0.22") | 6.4mm (0.25″) |  |

|                                                            |         |        |               |               |  |

|                                                            |         |        | LENGTH        | WIDTH         |  |

| High Specify Design:Lecture-3 © Rashad.M.Ramzan 2010-11 39 |         |        |               |               |  |

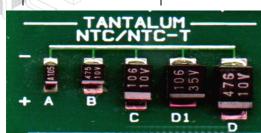

### Surface Mount Tantalum Electrolytic Capacitors

| Case Code           | Metric    | English | Length        | Width         |

|---------------------|-----------|---------|---------------|---------------|

| Р                   | 2012      | 0805    | 2.0mm (0.08″) | 1.2mm (0.05″) |

| <mark>A</mark> , A2 | 3216      | 1206    | 3.2mm (0.12″) | 1.6mm (0.06″) |

| <mark>B</mark> , B2 | 3528      | 1411    | 3.5mm (0.14") | 2.8mm (0.11") |

| С                   | 6032      | 2412    | 6.0mm (0.24") | 3.2mm(0.12")  |

| D1*                 | 5846      | 2318    | 5.8mm (0.23") | 4.6mm(0.18″)  |

| D, E                | 7343      | 2917    | 7.3mm (0.29″) | 4.3mm (0.17″) |

| * - D1 is Japa      | nese size |         |               |               |

© Rashad.M.Ramzan 2010-11

# Surface Mount Film Chip Capacitors

| <u> </u>           | Metric        | Length            | Width                |

|--------------------|---------------|-------------------|----------------------|

| 0805               | 2012          | 2.0mm (0.08")     | 1.2mm (0.05″)        |

| 1206               | 3216          | 3.2mm (0.12")     | 1.6mm (0.06″)        |

| 1210               | 3225          | 3.2mm (0.12")     | 2.5mm (0.10″)        |

| 1913               | 4833          | 4.8mm (0.19")     | 3.3mm (0.13")        |

| 2416               | 6041          | 6.0mm (0.24")     | 4.1mm (0.16")        |

|                    |               |                   |                      |

|                    |               |                   | No Component Marking |

| High Speed PCB Des | ign:Lecture-3 | © Rashad.M.Ramzar | n 2010-11 41         |

|                    |               |                   |                      |

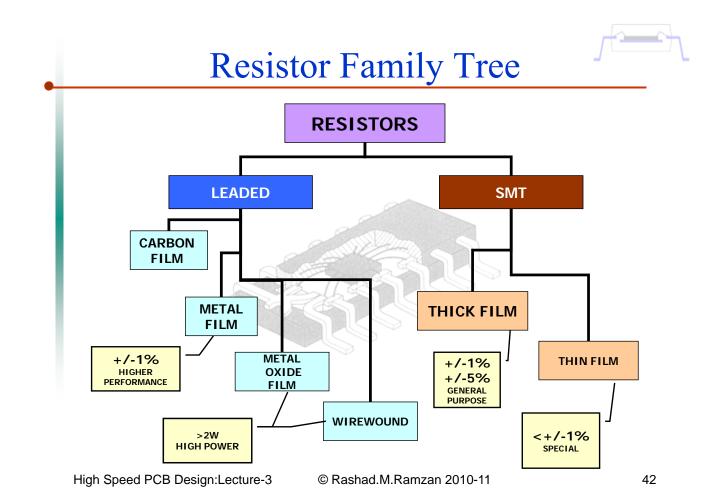

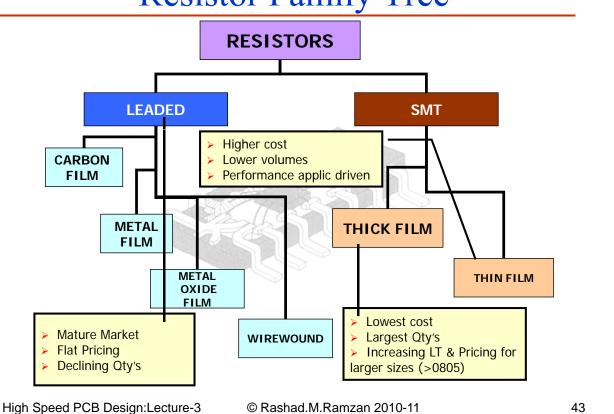

### **Resistor Family Tree**

### **SMD** Resistor Sizes English Metric Length Width 0201 0502 0.5mm (0.02") 0.25mm (0.01") 0402 1005 1.0mm (0.04") 0.5mm (0.02") 0603 1608 1.6mm (0.06") 0.8mm (0.03") 0805 2012 2.0mm (0.08") 1.2mm (0.05") 1206 3216 3.2mm (0.12") 1.6mm (0.06") Circuit Type "I" Circuit Type "I" 1210 3.2mm (0.12") 3225 2.5mm (0.10") Isolated Isolated 1812 4532 4.5mm (0.18") 3.2mm (0.12") 2225 5764 5.7mm (0.22") 6.4mm (0.25") NRC Thick Film Chips NRSN 6**1** Circuit Type "C" Circuit Type "D" Bussed/Common Bussed/Common

High Speed PCB Design:Lecture-3

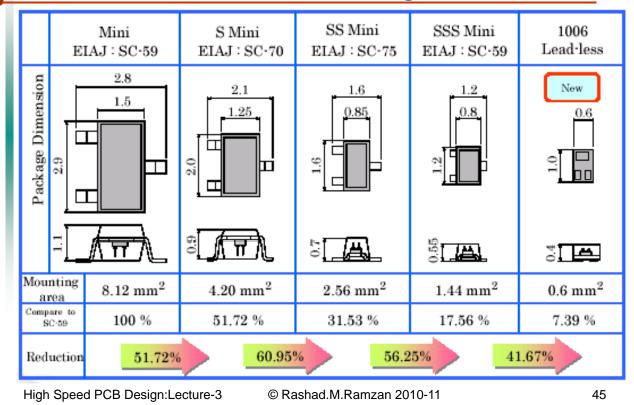

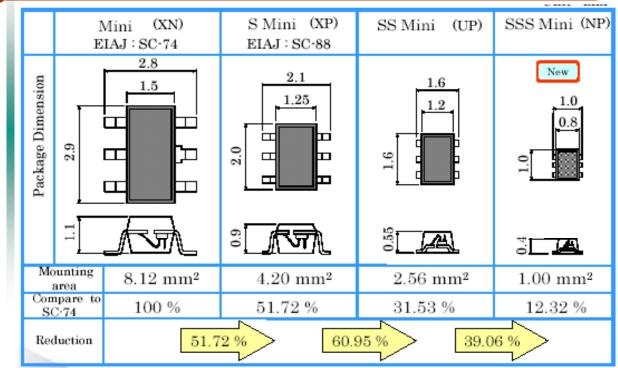

### **Discrete Packages**

### **Discrete Packages**

High Speed PCB Design:Lecture-3

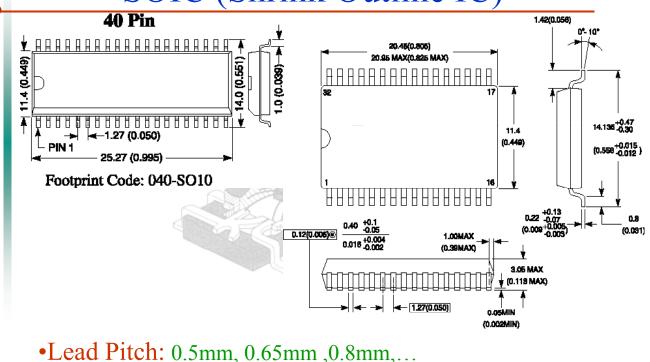

# SOIC (Shrink Outline IC)

High Speed PCB Design:Lecture-3 © Rashad.M.Ramzan 2010-11

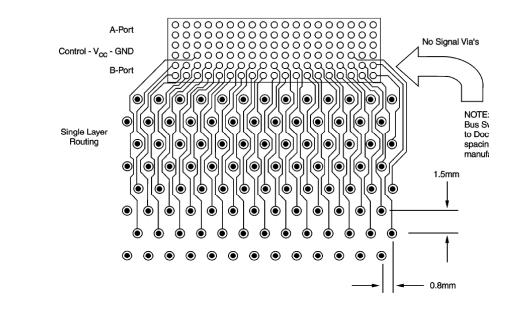

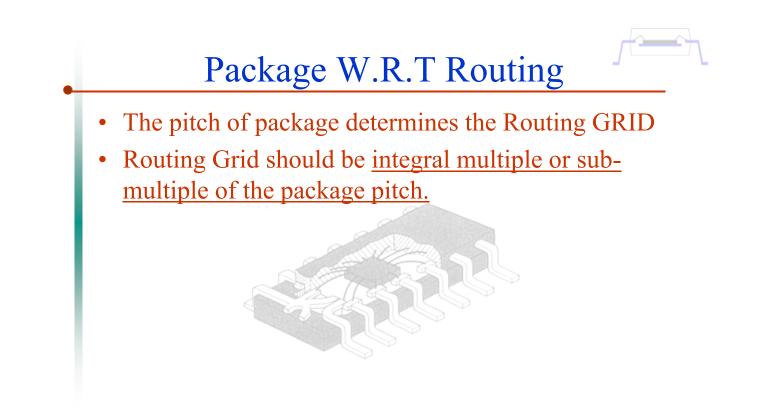

IC Package Pitch & Routing Grid

- Grid: An invisible imaginary mesh on which we can place the traces on the PCB board. Size of grid depends upon component pitch, no of traces, no of I.Os and routing space available.

- Routing the traces is preferred to be on grid.

- Easy to rout by hand and modify.

- Auto router performs faster on bigger grids but do not route 100% traces.

- Easy to reroute and rip off.

- If possible choose the package with same pitch size or some even multiple factor.

High Speed PCB Design:Lecture-3

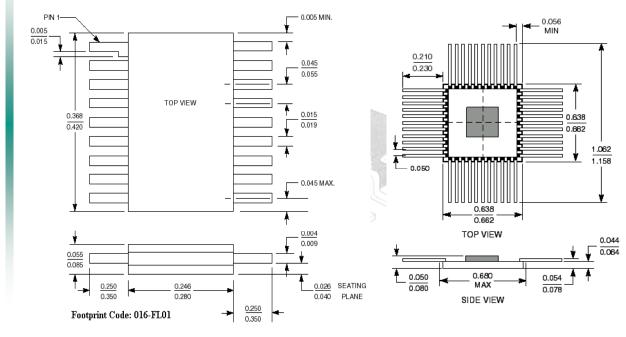

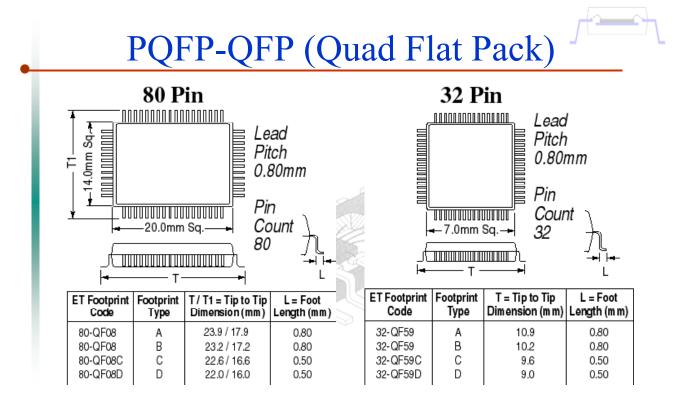

## Flat-pack Footprints

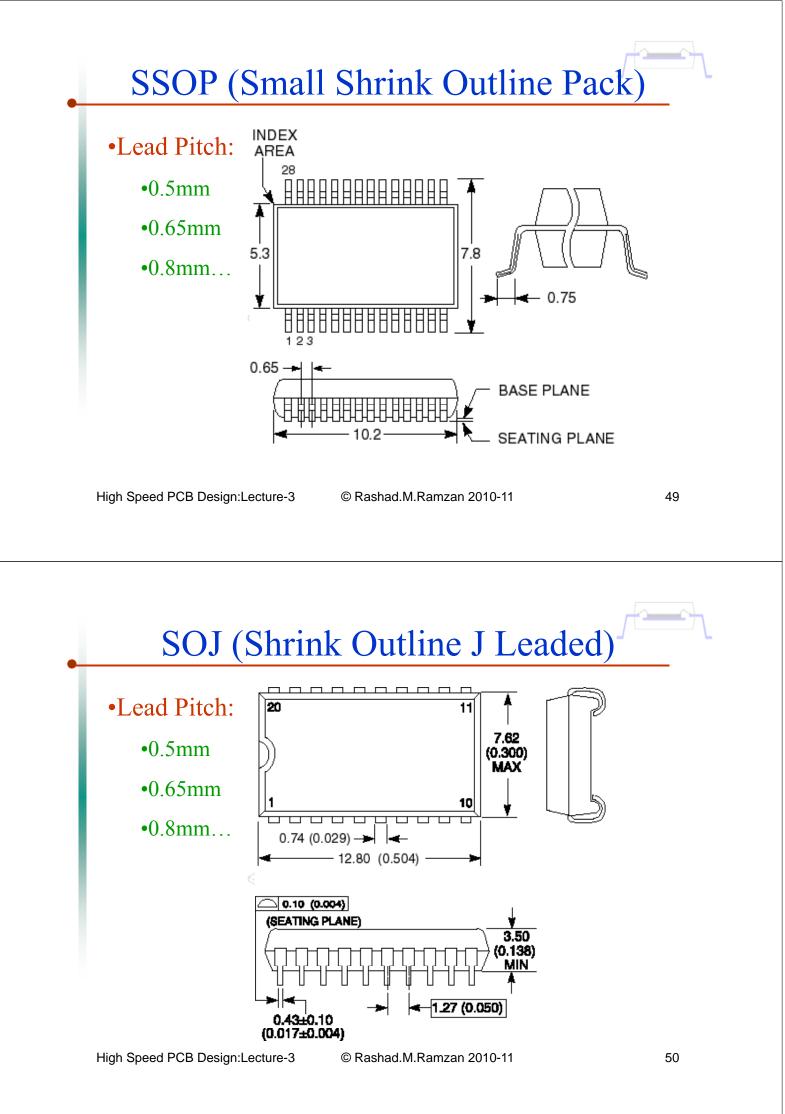

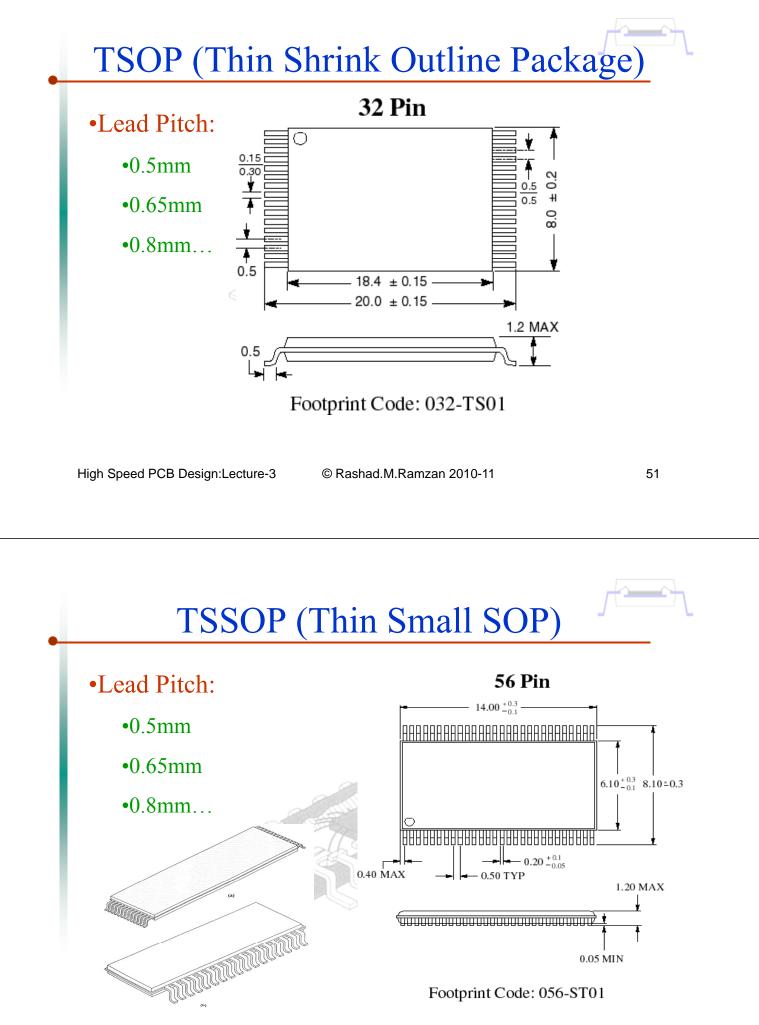

### •Lead Pitch: 0.5mm, 0.65mm, 0.8mm,...

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

53

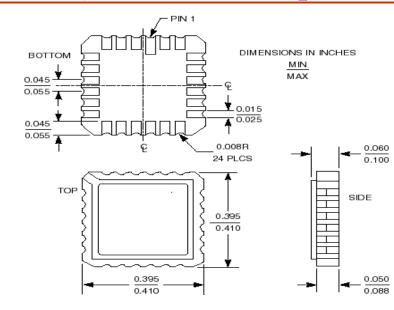

### LCC (Lead Less Chip Carrier)

•Lead Pitch: 0.5mm, 0.65mm, 0.8mm,...

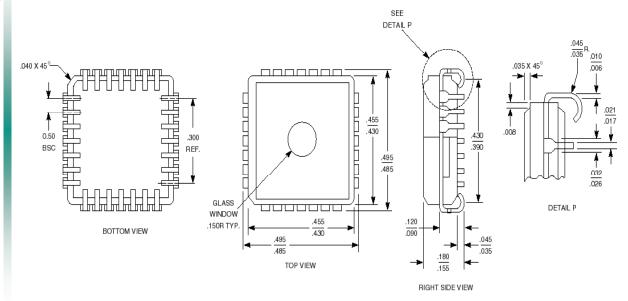

# JLCC (J Leaded Chip Carrier)

JEDEC REF. MO-087AA

### •Lead Pitch: 0.5mm, 0.65mm, 0.8mm,...

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

55

### •Lead Pitch: 0.5mm, 0.65mm, 0.8mm,...

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

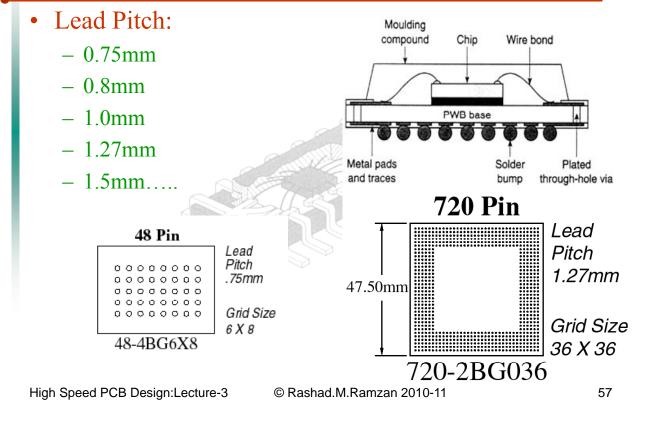

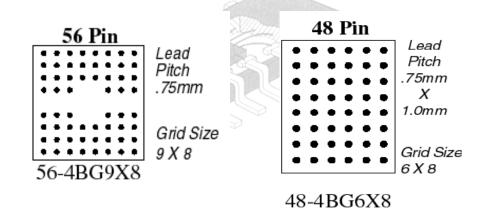

## BGA (Ball Grid Array)

### U-BGA

| Pin Count | Grid Size | Lead Pitch    |

|-----------|-----------|---------------|

| 40        | 5 x 8     | .75mm x 1.0mm |

| 48        | 6 x 8     | .75mm x 1.0mm |

| 56        | 9 x 8     | .75mm x 1.0mm |

### •Lead Pitch: 0.75mm, 0.8mm ,1.0mm

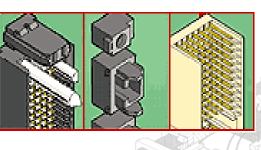

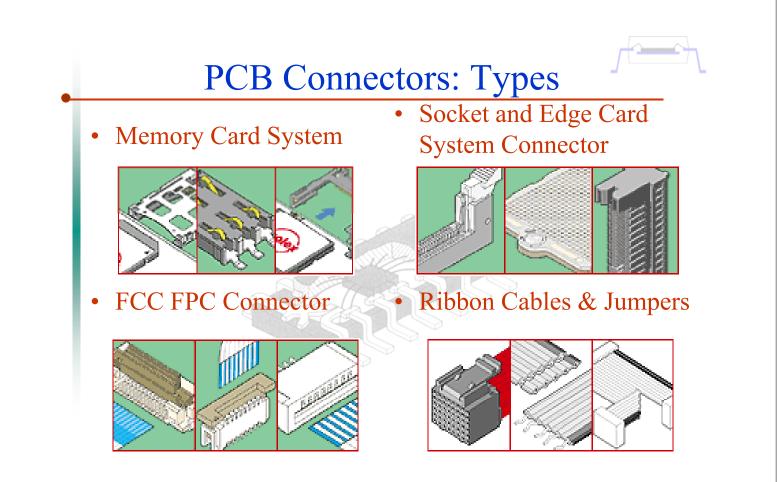

## PCB Connectors: Types

• Back Plane

Board to Board

High Speed PCB Design:Lecture-3

• Wire to Board

- Wire to Wire

- © Rashad.M.Ramzan 2010-11

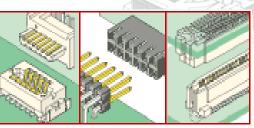

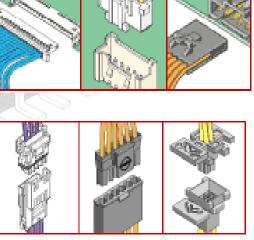

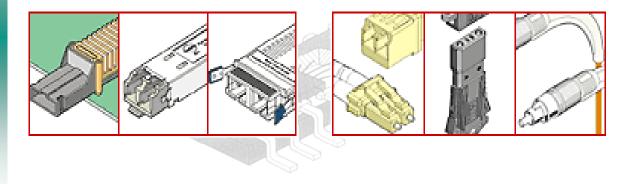

# PCB Connectors: Types

<image>

Wire trap connector

Modular Plugs and Jacks

Image: Connectors

Shielded Connectors

FF- Microwave Connector

Image: Connec

© Rashad.M.Ramzan 2010-11

- High Speed PCB Design:Lecture-3

- <section-header><section-header><text><text><image><image><image><image>

# Fiber Optic Connector: Types

• Optoelectronics connectors

Passive Connectors

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

63

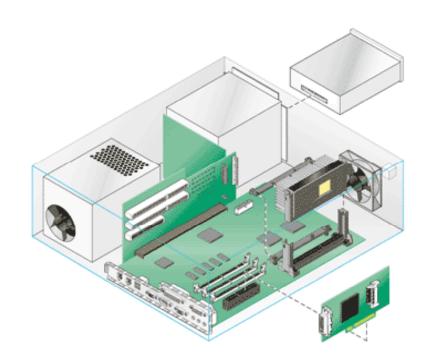

### Different Type of Connectors and Cables in a Product

### Connectors

Current path in a connector with several drivers.

High Speed PCB Design:Lecture-3

Drivers

© Rashad.M.Ramzan 2010-11

Receivers

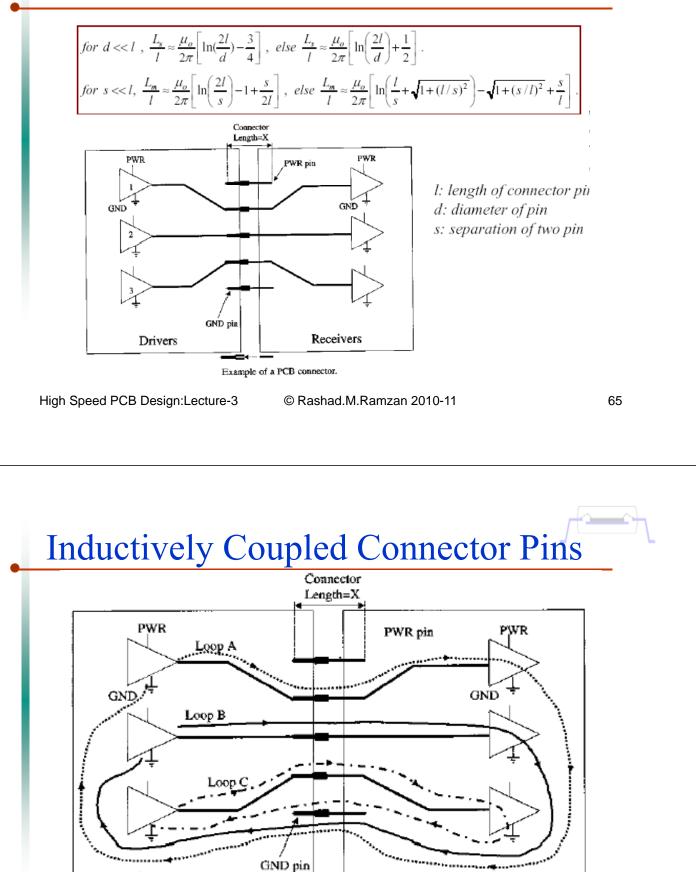

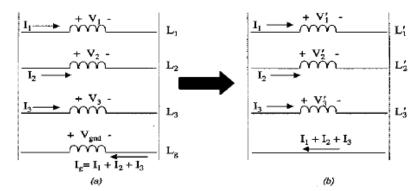

## Effective Inductance of Conductor Pins

Incorporating return inductance into the signal conductor: (a) three inductive signal pins coupled to an inductive ground return pin; (b) effect of the ground return pin.

High Speed PCB Design:Lecture-3

Effective inductance of each pin © Rashad.M.Ramzan 2010-11

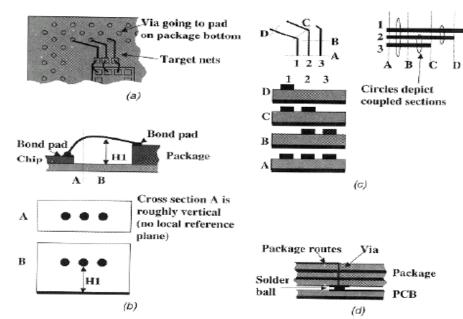

### Package Parasitic Modeling

Components of a package: (a) modeling a BGA package; (b) attachment of die to package; (c) on-package routing: (d) connection to PCB.

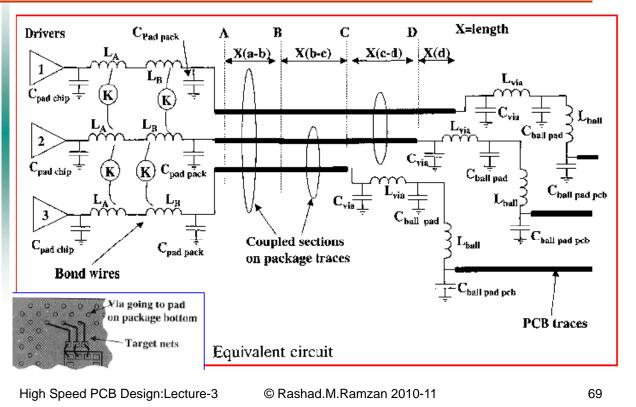

### Package Parasitic Modeling: EQ Circuit

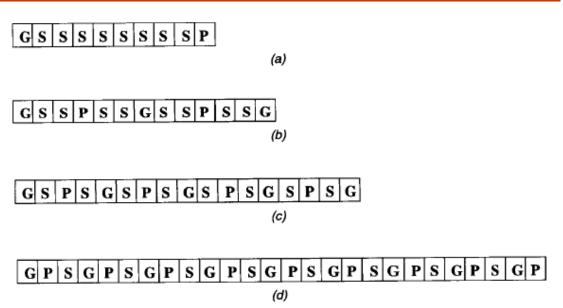

Example: Connector Pin Pattern for 8-pin Pattern

Eight-bit connector pin-out options assuming return current is flowing through both the power and ground pins: (a) inferior; (b) improved; (c) more improved; (d) optimal. G, ground pin; P, power pin; S, signal pin.

## Rule of Thumbs For Connector

- Connector selection

- Data sheets provide –3db loss bandwidth, x-talk figures and impedance value.

- Select the –3db BW for at least > third harmonic of signal depending upon RISE time not BUS speed.

- Minimize the physical length of connector pins

- Maximize the ratio of power and GND pins to signal pins, if possible this ratio should be one.

- Place each signal pin as close as possible to current return pin.

- Place power pins adjacent to ground pins.

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

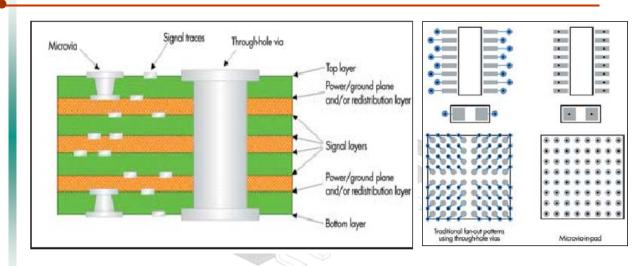

Via and Micro-via

- Micro Via is blind via with diameter < 5 mil

- Used in highly Dense boards inside pads with laser drilling

- Recommended for designs with 200 IO pins/sq in

75

0.009" 0.009"

14:1

## Standard Via Sizes

| Table 1 – Standard hole sizes for a typical fabricator |                     |                     |  |  |

|--------------------------------------------------------|---------------------|---------------------|--|--|

|                                                        | Standard            | Engineering         |  |  |

| Minimum Finished Hole Size                             | 0.008"              | 0.006"              |  |  |

| Minimum Drill Size                                     | 0.01"               | 0.008"              |  |  |

| Minimum Required Pad                                   | Drill size + 0.014" | Drill size + 0.010" |  |  |

| Resulting Annular Ring                                 | 0.001 "             | Tangency            |  |  |

Minimum Drill to Plane Clearance 0.012" Minimum Drill to Trace (Internal) 0.01" Maximum Apect Ratio 10:1

### Table 2 – Laser drilling capabilities of an advanced PCB facility

| Minimum Finished Hole Size<br>Minimum Drill Size<br>Minimum Required Pad<br>Resulting Annular Ring<br>Minimum Drill to Plane Clearance<br>Minimum Drill to Trace (Internal) | Standard<br>0.002"<br>0.006"<br>0.012"<br>Tangency<br>0.01"<br>0.01" | Engineering<br>0.001"<br>0.004"<br>0.008"<br>Tangency<br>0.008"<br>0.008" |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|

| Minimum Drill to Trace (Internal)<br>Apect Ratio                                                                                                                            | 0.01"<br>1:1                                                         | 0.008"<br>1:1                                                             |

| High Speed PCB Design:Lecture-3                                                                                                                                             | © Rashad.M.Ramzan 2010-11                                            |                                                                           |

Via: Aspect ratio and Tear Drops

Figure 1 – A pad with (right) and without (left) a teardrop. Teardropping provides a strong hole-to-trace connection Figure 2 – A pad with a good aspect ratio (at top) is characterized by a hole diameter in proportion to the hole depth, which facilitates uniform plating. A hole that is too narrow or deep (bottom) is harder to plate

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11

### Summary

- Why is packaging important ?

- Trends in packaging

- Impact on high speed signals

- Package and connector models

- IC packages

- Through hole

- Surface mount

- Connectors

- Surface mount

- Through hole

- Via and Via Types

- Via Modeling

- Standard Sizes, HDI

High Speed PCB Design:Lecture-3

© Rashad.M.Ramzan 2010-11